Then click Tools > Run EDA Simulation Tools > EDA RTL Simulation

Set your module as the top level module, compile.

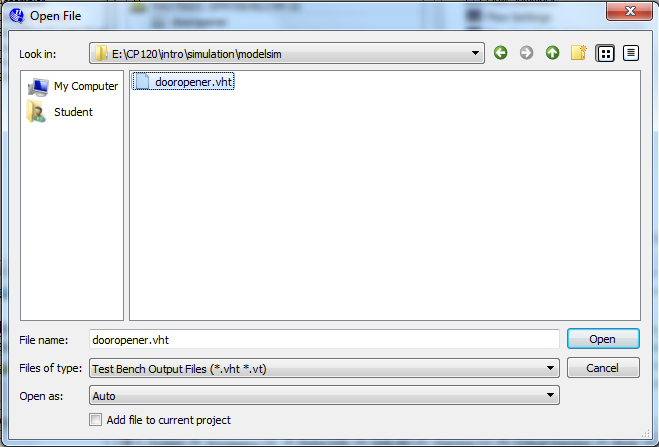

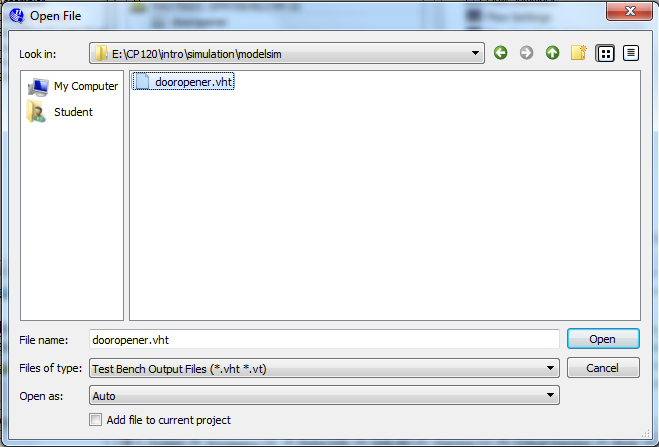

testbench)Īdd the file containing your testbench module. Select Compile testbench: name of the top level module (e.g.

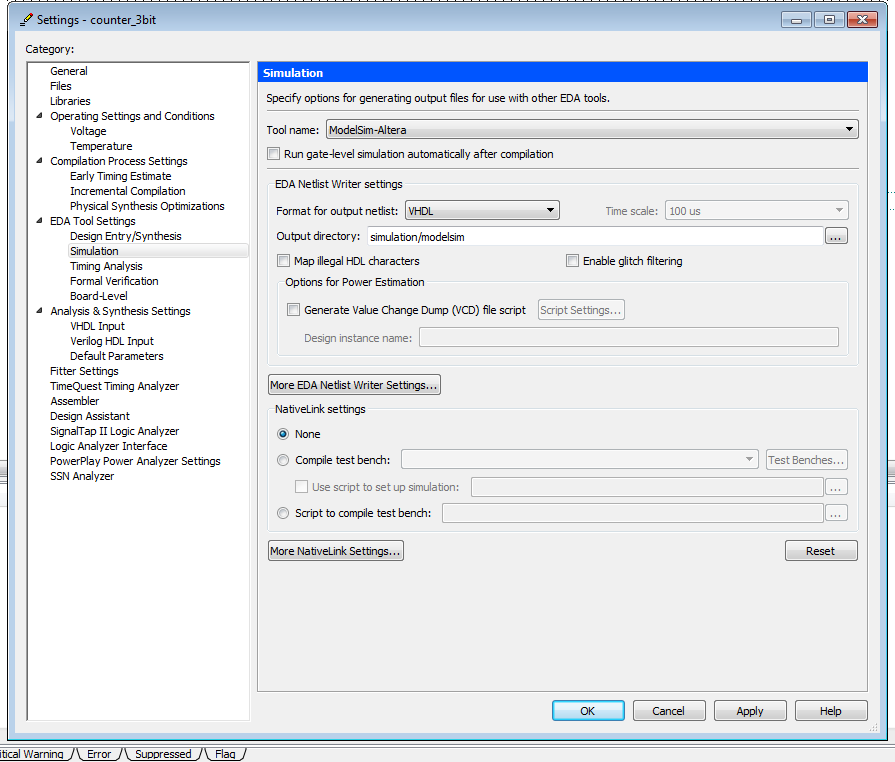

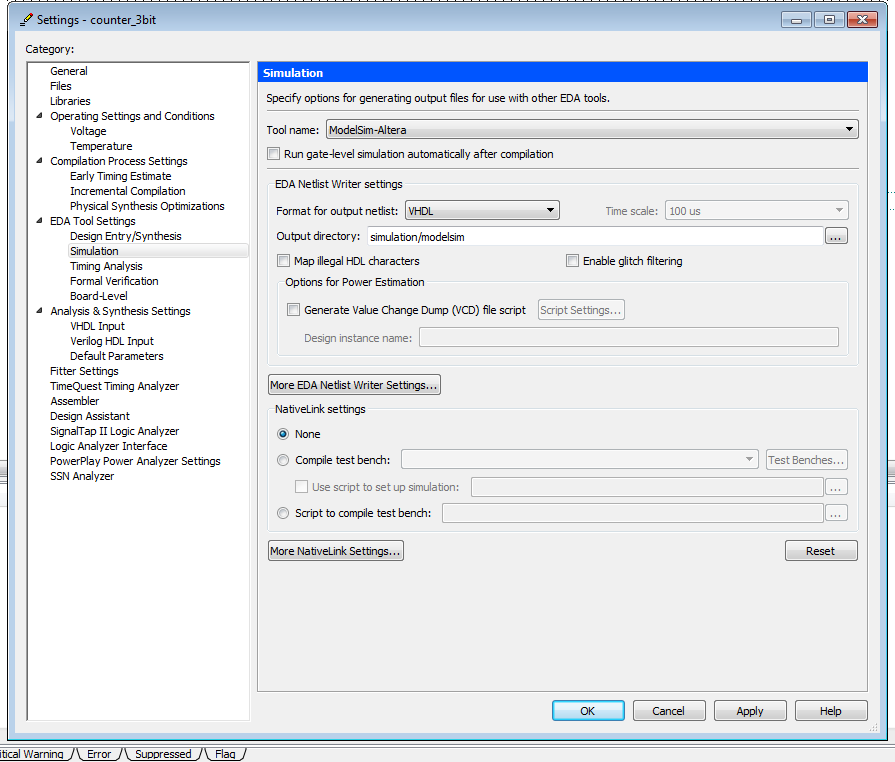

Assignments > Settings > EDA Tool Settings > Simulationįormat for output netlist: The language you wrote the testbench in. I like to put in some form of index that correlates with clock ticks. Modelsim can only simulate modules that you have the verilog files for. M4K blocks are simulated as having registered outputs. Create inputs for the device under test (DUT), usually reset, play, input(s), output(s), etc. Since testbenches are usually not synthesized, you can use initial blocks. Note you can never have a resolution that is lower than the length of the tick though If you want to speed up your simulation, make the resolution lower. Because of `timescale 1ns/ 1ps, max precision of 1ps, or. Because of `timescale 1ns /1ps, #22 will be translated to 22 ns. timescale indicates what the length of a “tick” is and the resolution of “ticks”. Some key components of a testbench module:.

Step 1: Write a Testbench in Verilog/VHDL I have tried to only include what is useful. If you want more tips and tricks read the additional comments. The main points are underlined and numbered. This is a quick and dirty guide to getting modelsim working with Quartus.

#MODELSIM TESTBENCH TUTORIAL CODE#

Modelsim is a powerful tool used to simulate Verilog or VHDL code that you have written. The Quick and Dirty Guide to Using ModelSim with Quartus - Julie Wang 2014

0 kommentar(er)

0 kommentar(er)